オンボードメモリインタフェース

オンボードメモリインターフェイスは、AMBA AXI4ストリームプロトコルスペックに基づいています。

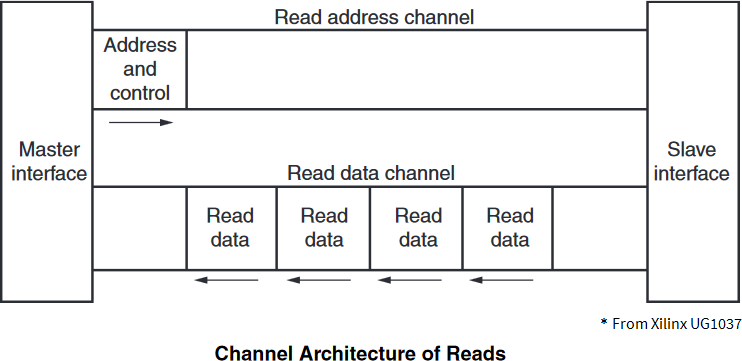

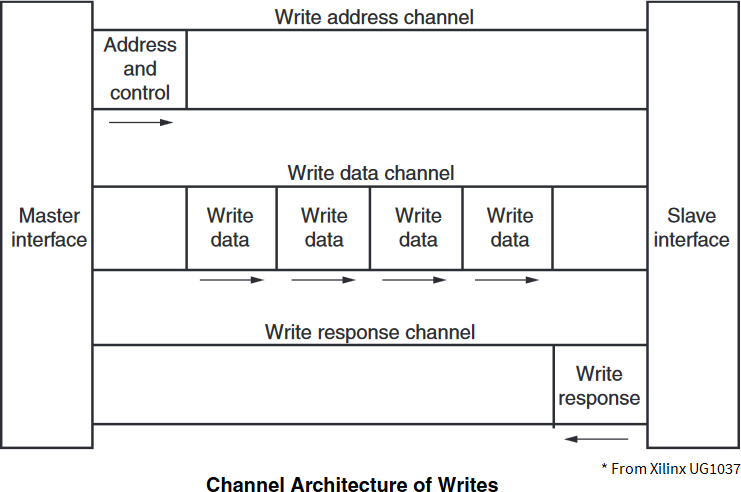

AXI4は次の、5つのチャネルで構成されるメモリマップインターフェイスです。

| □ | 書き込みアドレスチャネル |

| □ | 書き込みデータチャネル |

| □ | 書き込み応答チャネル |

| □ | 読み込みアドレスチャネル |

| □ | 読み込みデータチャネル |

データはマスタとスレーブの間を同時に双方向に移動でき、データ転送サイズは異なります。AXI4の制限は、最大256データ転送のバーストトランザクションです。

次のセクションでは、AXI4信号について簡単に説明します。

信号、インターフェイス要件、およびトランザクション属性の詳細については、www.amba.comのAMBA AXIおよびACEプロトコルスペックを参照してください。

|

信号 |

幅 | 指示 |

説明 |

|---|---|---|---|

|

m_axi_resetn |

1 | 入力 |

RESETnによってAXI4インターフェイスがリセットされます。 |

|

信号 |

幅 |

指示 |

説明 |

||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

m_axi_awaddr |

32 |

出力 |

アドレスを書き込む。書き込みアドレスは、書き込みバーストトランザクションの最初の転送のアドレスを示します。 |

||||||||||||

|

m_axi_awlen |

8 |

出力 |

バースト長。バースト長は、バースト内の正確な転送数を示します。この情報は、アドレスに関連したデータ転送の数を決定します。 Burst_Length(バースト長) = AWLEN[7:0] + 1 |

||||||||||||

|

m_axi_awsize |

3 |

出力 |

バーストサイズ。この信号はバースト内の各転送のサイズをバイト単位で示しています。 Burst_Size(バーストサイズ) = 2^AWSIZE[2:0] |

||||||||||||

|

m_axi_awburst |

2 |

出力 |

バーストタイプ。バーストタイプとサイズ情報は、バースト内の各転送のアドレスの計算方法を決定します。 Burst_Type(バーストタイプ): "00" = FIXED(固定); "01" = INCR(インクリメンタル); "10" = WRAP(ラップ) |

||||||||||||

|

m_axi_awlock |

1 |

出力 |

ロックタイプ。転送のアトミック特性に関する追加情報を提供します。 Atomic_Access(アトミックアクセス): '0’ 通常; '1’ 排他的 |

||||||||||||

|

m_axi_awcache |

4 |

出力 |

メモリタイプ。この信号は、トランザクションがシステム内でどのように進行する必要があるかを示します。 Memory_Attributes(メモリ属性):

|

||||||||||||

|

m_axi_awprot |

3 |

出力 |

保護タイプ。この信号は、トランザクションの権限とセキュリティレベル、およびトランザクションがデータアクセスか命令アクセスかを示します。 Access_Permissions(アクセス権限):

|

||||||||||||

|

m_axi_awqos |

4 |

出力 |

サービス品質、QoS。書き込みトランザクションごとに送信されたQoS ID。 Quality_of_Service(サービス品質):優先度 |

||||||||||||

|

m_axi_awvalid |

1 |

出力 |

アドレスを有効に書き込む。この信号は、チャネルが有効な書き込みアドレスと制御情報を通信していることを示します。 |

||||||||||||

|

m_axi_awready |

1 |

入力 |

アドレスをレディ状態に書き込む。この信号は、スレーブがアドレスと関連する制御信号を受け入れる準備ができていることを示します。 |

説明は、AMBA AXIおよびACEプロトコルスペックからの抜粋です。

|

信号 |

幅 |

指示 |

説明 |

|---|---|---|---|

|

m_axi_wdata |

W |

出力 |

データを書き込む。 |

|

m_axi_wstrb |

W/8 |

出力 |

ストローブを書き込む。この信号は、どのバイトレーンに有効なデータがあるかを示します。書き込みデータバスの8ビットごとに1つの書き込みストローブビットがあります。 |

|

m_axi_wlast |

1 |

出力 |

最後を書き込む。この信号は書き込みバーストの最後の転送を示します。 |

|

m_axi_wvalid |

1 |

出力 |

有効を書き込む。この信号は有効な書き込みデータとストローブが利用可能であることを示します。 |

|

m_axi_wready |

1 |

入力 |

レディを書き込む。この信号は、スレーブが書き込みデータを受け取れることを示します。 |

「幅」列の「W」は、書き込みデータチャネルのデータ幅であるMEMORY_DATA_WIDTHを示します。

| □ |

|

| □ |

|

| □ |

|

説明は、AMBA AXIおよびACEプロトコルスペックからの抜粋です。

|

信号 |

幅 |

指示 |

説明 |

||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

m_axi_bresp |

2 |

入力 |

応答を書き込む。この信号は書き込みトランザクションのステータスを示します。 応答:

|

||||||||||||

|

m_axi_bvalid |

1 |

入力 |

応答を有効に書き込む。この信号は、チャネルが有効な書き込み応答を通知していることを示します。 |

||||||||||||

|

m_axi_bready |

1 |

出力 |

応答の準備ができています。この信号は、マスタが書き込み応答を受け取れることを示します。 |

説明は、AMBA AXIおよびACEプロトコルスペックからの抜粋です。

用:m_axi_bresp

| □ | OKAY:通常のアクセスに成功しました。通常のアクセスが成功したことを示します。排他アクセスが失敗したことを示すこともできます。「OKAY:通常のアクセスに成功しました。」を参照ください。 |

| □ | EXOKAY:排他アクセスに成功しました。排他アクセスの読み取り部分または書き込み部分が成功したことを示します。 |

| □ | SLVERR:スレーブエラー。アクセスが正常にスレーブに到達した場合でも、スレーブが発信元のマスターにエラー状態を返したい場合に使用します。 |

| □ | DECERR:デコードエラー。トランザクションアドレスにスレーブがないことを示すために、通常はインターコネクトコンポーネントによって生成されます。 |

|

信号 |

幅 |

指示 |

説明 |

||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

m_axi_araddr |

32 |

出力 |

アドレスを読み込む。読み込みアドレスは、読み込みバーストトランザクションの最初の転送のアドレスを示します。 |

||||||||||||

|

m_axi_arlen |

8 |

出力 |

バースト長。バースト長は、バースト内の正確な転送数を示します。この情報は、アドレスに関連したデータ転送の数を決定します。 Burst_Length(バースト長) = ARLEN[7:0] + 1 |

||||||||||||

|

m_axi_arsize |

3 |

出力 |

バーストサイズ。この信号はバースト内の各転送のサイズをバイト単位で示しています。 Burst_Size(バーストサイズ) = 2^ARSIZE[2:0] |

||||||||||||

|

m_axi_arburst |

2 |

出力 |

バーストタイプ。バーストタイプとサイズ情報は、バースト内の各転送のアドレスの計算方法を決定します。 Burst_Type(バーストタイプ): "00" = FIXED(固定); "01" = INCR(インクリメンタル); "10" = WRAP(ラップ) |

||||||||||||

|

m_axi_arlock |

1 |

出力 |

ロックタイプ。転送のアトミック特性に関する追加情報を提供します。 Atomic_Access(アトミックアクセス): '0’ 通常; '1’ 排他的 |

||||||||||||

|

m_axi_arcache |

4 |

出力 |

メモリタイプ。この信号は、トランザクションがシステム内でどのように進行する必要があるかを示します。 Memory_Attributes(メモリ属性):

|

||||||||||||

|

m_axi_arprot |

3 |

出力 |

保護タイプ。この信号は、トランザクションの権限とセキュリティレベル、およびトランザクションがデータアクセスか命令アクセスかを示します。 Access_Permissions(アクセス権限):

|

||||||||||||

|

m_axi_arqos |

4 |

出力 |

サービス品質、QoS。書き込みトランザクションごとに送信されたQoS ID。 Quality_of_Service(サービス品質):優先度 |

||||||||||||

|

m_axi_arvalid |

1 |

出力 |

アドレスを有効に読み込む。この信号は、チャネルが有効な読み込みアドレスと制御情報を通信していることを示します。 |

||||||||||||

|

m_axi_arready |

1 |

入力 |

アドレスを有効に読み込む。この信号は、スレーブがアドレスと関連する制御信号を受け入れる準備ができていることを示します。 |

説明は、AMBA AXIおよびACEプロトコルスペックからの抜粋です。

|

信号 |

幅 |

指示 |

説明 |

|---|---|---|---|

|

m_axi_rdata |

W |

入力 |

データを読み込む。 |

|

m_axi_rresp |

2 |

入力 |

応答を読み込む。この信号は読み込み転送のステータスを示します。 応答: "00" = OKAY; "01" = EXOKAY; "10" = SLVERR; “11” = DECERR |

|

m_axi_rlast |

1 |

入力 |

最後を読み込む。この信号は読み込みバーストの最後の転送を示します。 |

|

m_axi_rvalid |

1 |

入力 |

有効に読み込む。この信号は、チャネルが必要な読み込みデータを通知していることを示します。 |

|

m_axi_rready |

1 |

出力 |

レディ状態を読み込む。この信号は、マスタが読み込みデータと応答情報を受け取れることを示します。 |

「幅」列の「W」は、書き込みデータチャネルのデータ幅であるMEMORY_DATA_WIDTHを示します。

| □ |

|

| □ |

|

| □ |

|

説明は、AMBA AXIおよびACEプロトコルスペックからの抜粋です。

有効/準備完了 ハンドシェイクタイミングチャート