온보드 메모리 인터페이스

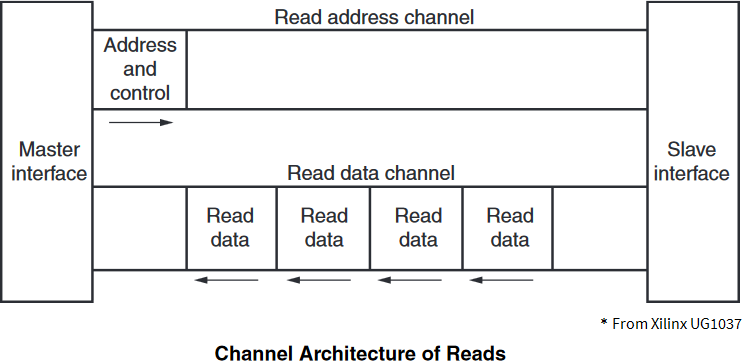

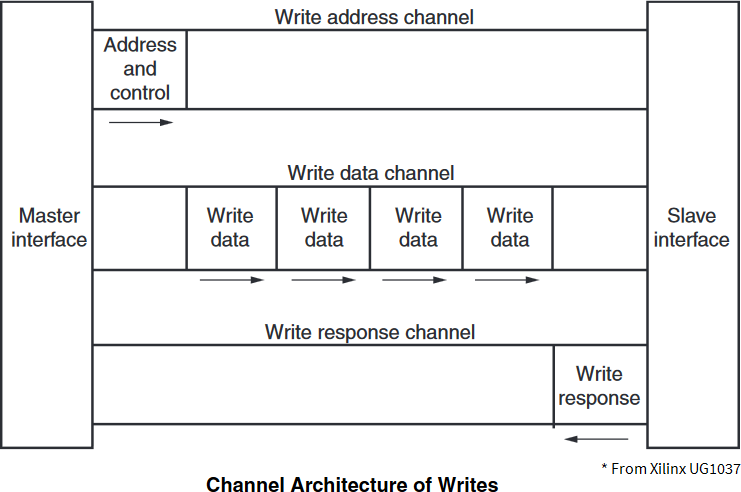

온보드 메모리 인터페이스는 AMBA AXI4-Stream 프로토콜 사양을 기반으로 합니다.

AXI4는 5개의 채널로 구성된 메모리 매핑 인터페이스입니다.

| □ | 주소 채널 쓰기 |

| □ | 데이터 채널 쓰기 |

| □ | 응답 채널 쓰기 |

| □ | 주소 채널 읽기 |

| □ | 데이터 채널 읽기 |

데이터는 마스터와 슬레이브 간에 동시에 양방향으로 이동할 수 있으며 데이터 전송 크기가 다를 수 있습니다.AXI4의 한계는 최대 256 데이터 전송의 버스트 트랜잭션입니다.

다음 섹션에서는 AXI4 신호에 대해 간략하게 설명합니다.

신호, 인터페이스 요구 사항 및 트랜잭션 속성에 대한 전체적인 내용은 www.amba.com에서 AMBA AXI 및 ACE Protocol Specification 문서를 참조하십시오.

|

신호 |

폭 | 방향 |

설명 |

|---|---|---|---|

|

m_axi_resetn |

1 | 입력 |

RESETn은 AXI4 인터페이스를 재설정합니다. |

|

신호 |

폭 |

방향 |

설명 |

||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

m_axi_awaddr |

32 |

출력 |

주소 쓰기.주소 쓰기는 버스트 트랜잭션 쓰기에서 첫 번째 전송 주소를 제공합니다. |

||||||||||||

|

m_axi_awlen |

8 |

출력 |

버스트 길이.버스트 길이는 정확한 버스트 전송 횟수를 나타냅니다.이 정보는 주소와 관련된 데이터 전송 수를 결정합니다. Burst_Length = AWLEN[7:0] + 1 |

||||||||||||

|

m_axi_awsize |

3 |

출력 |

버스트 크기.이 신호는 버스트의 각 전송 크기를 바이트로 나타냅니다. 버스트 크기 = 2^AWSIZE[2:0] |

||||||||||||

|

m_axi_awburst |

2 |

출력 |

버스트 유형.버스트 유형 및 크기 정보는 버스트 내의 각 전송에 대한 주소 계산 방법을 결정합니다. Burst_Type: "00" = FIXED; "01" = INCR; "10" = WRAP |

||||||||||||

|

m_axi_awlock |

1 |

출력 |

잠금 유형.전송의 원자적 특성에 대한 추가 정보를 제공합니다. Atomic_Access : '0'정상; '1'독점 |

||||||||||||

|

m_axi_awcache |

4 |

출력 |

메모리 유형.이 신호는 트랜잭션이 시스템을 통해 진행되는 데 필요한 방식을 나타냅니다. Memory_Attributes:

|

||||||||||||

|

m_axi_awprot |

3 |

출력 |

보호 유형.이 신호는 트랜잭션의 특권 및 보안 레벨과 트랜잭션이 데이터 액세스인지 또는 명령 액세스인지 여부를 나타냅니다. Access_Permissions:

|

||||||||||||

|

m_axi_awqos |

4 |

출력 |

서비스 품질, QoS.각 쓰기 트랜잭션에 대해 전송된 QoS 식별자입니다. Quality_of_Service: 우선 순위 수준 |

||||||||||||

|

m_axi_awvalid |

1 |

출력 |

올바른 주소 쓰기.이 신호는 채널이 유효한 쓰기 주소 및 제어 정보를 신호하고 있음을 나타냅니다. |

||||||||||||

|

m_axi_awready |

1 |

입력 |

주소 쓰기 준비.이 신호는 슬레이브가 주소 및 관련 제어 신호를 받아들일 준비가되었음을 나타냅니다. |

설명은 AMBA AXI 및 ACE 프로토콜 사양에서 발췌한 것입니다.

|

신호 |

폭 |

방향 |

설명 |

|---|---|---|---|

|

m_axi_wdata [*] |

W |

출력 |

데이터 쓰기. |

|

m_axi_wstrb |

W/8 |

출력 |

스트로브 쓰기.이 신호는 유효한 데이터를 보유하고 있는 바이트 레인을 나타냅니다.데이터 쓰기 버스의 각 8비트에 대해 하나의 스트로브 쓰기 비트가 있습니다. |

|

m_axi_wlast |

1 |

출력 |

마지막 쓰기.이 신호는 버스트 쓰기의 마지막 전송을 나타냅니다. |

|

m_axi_wvalid |

1 |

출력 |

쓰기 유효.이 신호는 유효 쓰기 데이터 및 스트로브를 사용할 수 있음을 나타냅니다. |

|

m_axi_wready |

1 |

입력 |

쓰기 준비.이 신호는 슬레이브가 데이터 쓰기를 받아들일 수 있음을 나타냅니다. |

너비 열에서 : "W"는 쓰기 데이터 채널의 데이터 너비인 MEMORY_DATA_WIDTH를 나타냅니다.

| □ |

|

| □ |

|

| □ |

|

설명은 AMBA AXI 및 ACE 프로토콜 사양에서 발췌한 것입니다.

|

신호 |

폭 |

방향 |

설명 |

||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

m_axi_bresp |

2 |

입력 |

응답 쓰기.이 신호는 트랜잭션 쓰기 상태를 나타냅니다. 응답:

|

||||||||||||

|

m_axi_bvalid |

1 |

입력 |

올바른 응답 쓰기.이 신호는 채널이 올바른 응답 쓰기를 신호하고 있음을 나타냅니다. |

||||||||||||

|

m_axi_bready |

1 |

출력 |

응답 준비.이 신호는 마스터가 쓰기 응답을 받아들일 수 있음을 나타냅니다. |

설명은 AMBA AXI 및 ACE 프로토콜 사양에서 발췌한 것입니다.

m_axi_bresp의 경우:

| □ | OKAY: 정상 액세스 성공.정상적인 액세스가 성공했음을 나타냅니다.독점적인 액세스가 실패했음을 나타낼 수도 있습니다.정상적인 액세스 성공을 확인합니다. |

| □ | EXOKAY: 독접 액세스 확인.독점 액세스의 읽기 또는 쓰기 부분이 성공적으로 완료되었음을 나타냅니다. |

| □ | SLVERR: 슬레이브 오류.액세스가 슬레이브에 성공적으로 도달했지만 슬레이브가 원래 마스터에 오류 조건을 반환하고자할 때 사용됩니다. |

| □ | DECERR: 디코더 오류.트랜잭션 주소에 슬레이브가 없음을 나타내기 위해 일반적으로 상호 연결 구성 요소로 생성합니다. |

|

신호 |

폭 |

방향 |

설명 |

||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

m_axi_araddr |

32 |

출력 |

주소 읽기.주소 읽기는 버스트 트랜잭션 읽기에서 첫 번째 전송 주소를 제공합니다. |

||||||||||||

|

m_axi_arlen |

8 |

출력 |

버스트 길이.버스트 길이는 정확한 버스트 전송 횟수를 나타냅니다.이 정보는 주소와 관련된 데이터 전송 수를 결정합니다. Burst_Length = ARLEN[7:0] + 1 |

||||||||||||

|

m_axi_arsize |

3 |

출력 |

버스트 크기.이 신호는 버스트의 각 전송 크기를 바이트로 나타냅니다. 버스트 크기 = 2^ARSIZE[2:0] |

||||||||||||

|

m_axi_arburst |

2 |

출력 |

버스트 유형.버스트 유형 및 크기 정보는 버스트 내의 각 전송에 대한 주소 계산 방법을 결정합니다. Burst_Type: "00" = FIXED; "01" = INCR; "10" = WRAP |

||||||||||||

|

m_axi_arlock |

1 |

출력 |

잠금 유형.전송의 원자적 특성에 대한 추가 정보를 제공합니다. Atomic_Access : '0'정상; '1'독점 |

||||||||||||

|

m_axi_arcache |

4 |

출력 |

메모리 유형.이 신호는 트랜잭션이 시스템을 통해 진행되는 데 필요한 방식을 나타냅니다. Memory_Attributes:

|

||||||||||||

|

m_axi_arprot |

3 |

출력 |

보호 유형.이 신호는 트랜잭션의 특권 및 보안 레벨과 트랜잭션이 데이터 액세스인지 또는 명령 액세스인지 여부를 나타냅니다. Access_Permissions:

|

||||||||||||

|

m_axi_arqos |

4 |

출력 |

서비스 품질, QoS.각 쓰기 트랜잭션에 대해 전송된 QoS 식별자입니다. Quality_of_Service: 우선 순위 수준 |

||||||||||||

|

m_axi_arvalid |

1 |

출력 |

올바른 주소 읽기.이 신호는 채널이 올바른 읽기 주소 및 제어 정보를 신호하고 있음을 나타냅니다. |

||||||||||||

|

m_axi_arready |

1 |

입력 |

주소 읽기 준비.이 신호는 슬레이브가 주소 및 관련 제어 신호를 받아들일 준비가되었음을 나타냅니다. |

설명은 AMBA AXI 및 ACE 프로토콜 사양에서 발췌한 것입니다.

|

신호 |

폭 |

방향 |

설명 |

|---|---|---|---|

|

m_axi_rdata |

W |

입력 |

읽기 데이터. |

|

m_axi_rresp |

2 |

입력 |

응답 읽기.이 신호는 읽기 전송의 상태를 나타냅니다. 응답: "00" = OKAY; "01" = EXOKAY; "10" = SLVERR; “11” = DECERR |

|

m_axi_rlast |

1 |

입력 |

마지막 읽기.이 신호는 버스트 읽기의 마지막 전송을 나타냅니다. |

|

m_axi_rvalid |

1 |

입력 |

올바른 읽기.이 신호는 채널이 필요한 읽기 데이터를 신호하고 있음을 나타냅니다. |

|

m_axi_rready |

1 |

출력 |

읽기 준비.이 신호는 마스터가 읽기 데이터 및 응답 정보를 받아 들일 수 있음을 나타냅니다. |

너비 열에서 : "W"는 쓰기 데이터 채널의 데이터 너비인 MEMORY_DATA_WIDTH를 나타냅니다.

| □ |

|

| □ |

|

| □ |

|

설명은 AMBA AXI 및 ACE 프로토콜 사양에서 발췌한 것입니다.

올바른/준비 핸드셰이크 타이밍 다이어그램